ZYNQ(FPGA)与DSP之间GPIO通讯

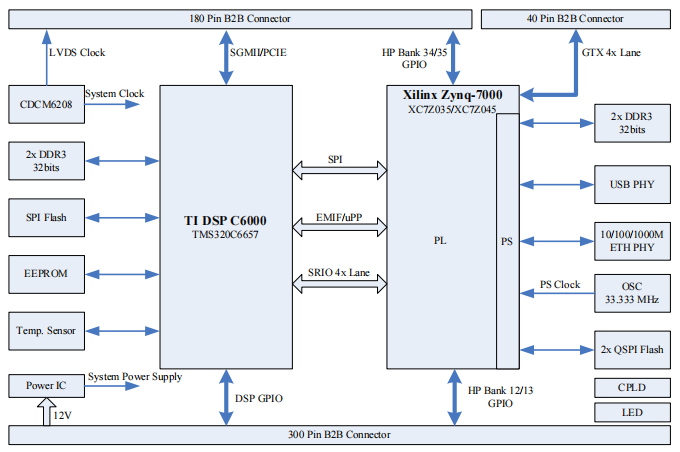

原创本文主要介绍说明XQ6657Z35-EVM 高速数据处理评估板ZYNQ(FPGA)与DSP之间GPIO通信的功能、使用步骤以及各个例程的运行效果。

1.1 ZYNQ (FPGA)与DSP之间GPIO通讯

1.1.1 例程位置

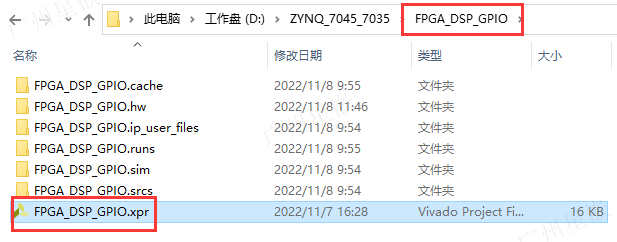

ZYNQ例程保存在资料盘中的Demo\ZYNQ\PL\FPGA_DSP_GPIO文件夹下。

DSP例程保存在资料盘中的Demo\DSP\XQ_GPIO_FPGA文件夹下。

1.1.2 功能简介

实现DSP与ZYNQ PL端之间GPIO接口传输功能。

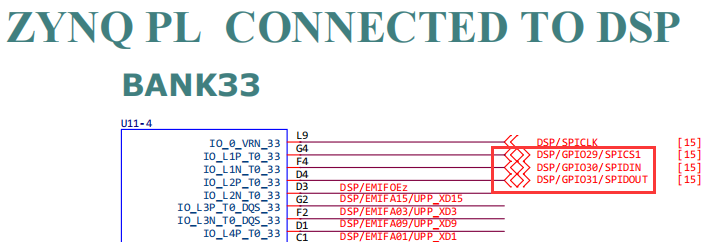

DSP与ZYNQ PL端之间有3根GPIO信号相连,如下原理图标注所示:

DSP示例通信程序将GPIO29、GPIO30两个GPIO设置为输出(对ZYNQ而言就是输入),GPIO31设置为输入(对ZYNQ而言就是输出)。DSP在GPIO29、GPIO30两个GPIO上产生方波信号,ZYNQ可通过ILA软逻辑分析仪抓取波形查看;ZYNQ通过VIO虚拟IO往GPIO31上输出高、低电平,DSP示例程序里面检测GPIO31下降沿中断,一旦检测到GPIO31管脚下降沿中断信号,则打印测试信息。

1.1.3 例程使用

1.1.3.1 加载运行ZYNQ程序

1.1.3.1.1 打开Vivado工程

打开Vivado示例工程:

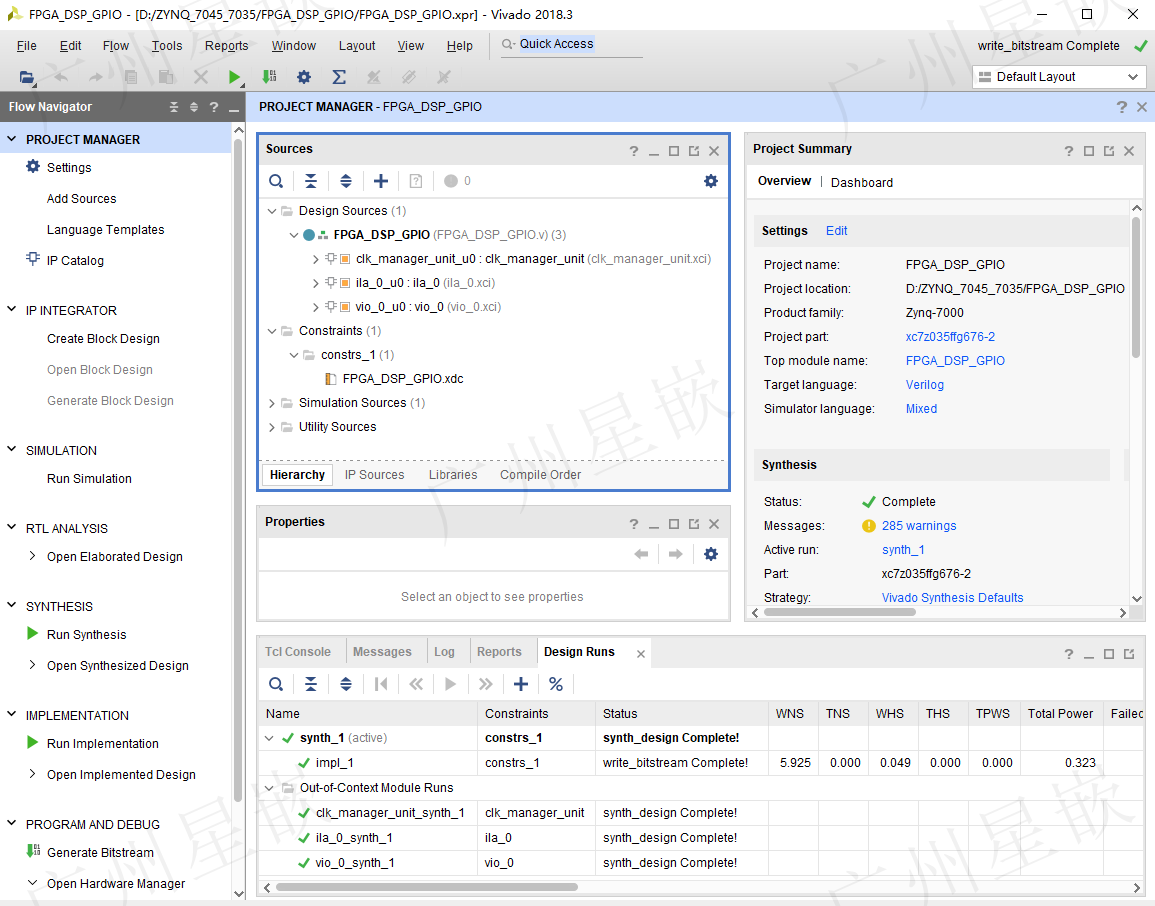

工程打开后界面如下图所示:

1.1.3.1.2 下载ZYNQ PL程序

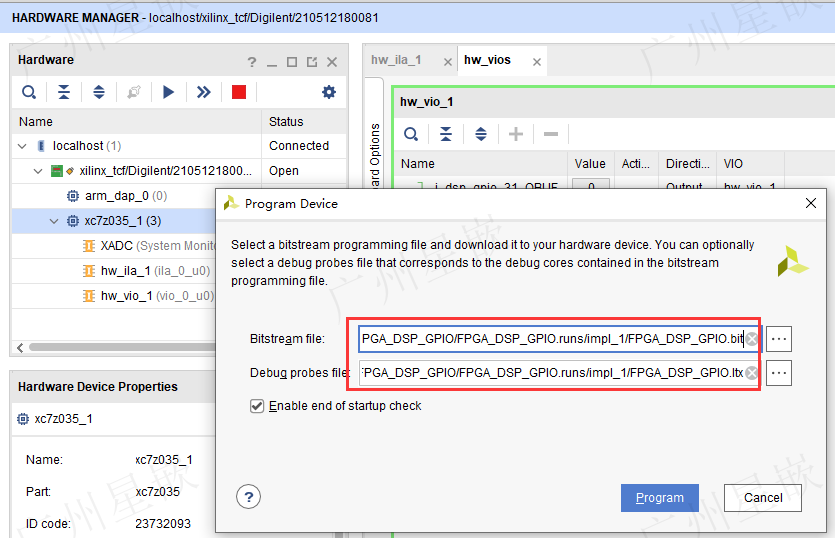

下载bit流文件FPGA_DSP_GPIO.bit,如下图下载界面所示:

1.1.3.2 加载运行DSP程序

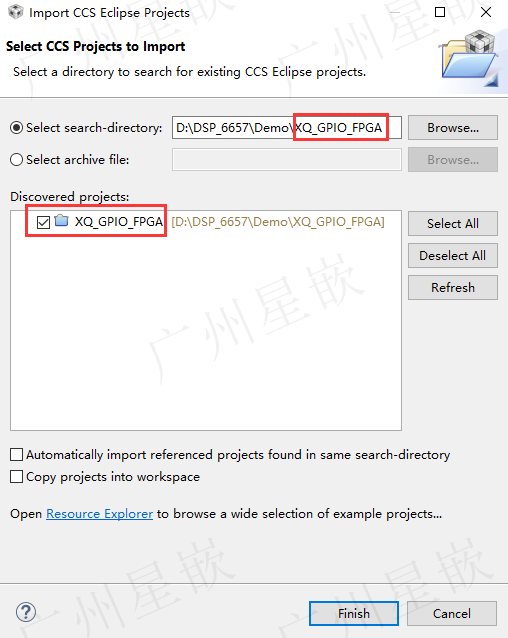

1.1.3.2.1 CCS导入例程

CCS软件导入示例工程XQ_GPIO_FPGA,如下图所示:

CCS示例工程导入后界面如下图所示:

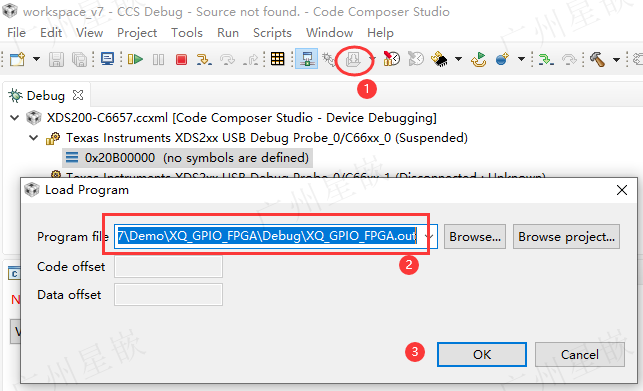

1.1.3.2.2 下载运行CCS程序

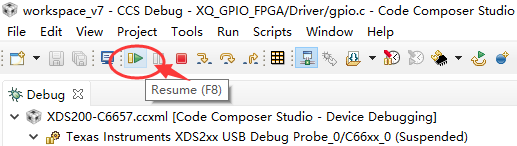

下载DSP可执行文件XQ_GPIO_FPGA.out:

点击Resume运行DSP程序:

1.1.3.3 运行结果说明

1.1.3.3.1 DSP程序运行结果

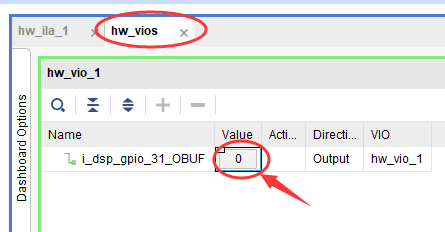

点击ZYNQ PL调试界面上hw_vios窗口中Value下面的数字0或1,从而在GPIO31上产生高低电平信号:

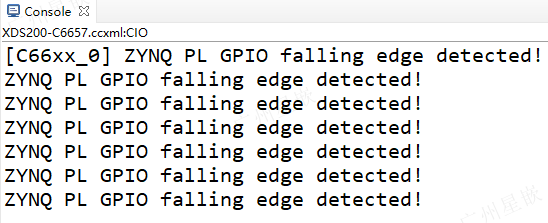

每当GPIO31上产生高低电平下降沿信号,DSP程序进入中断服务函数,打印如下图所示的信息:

1.1.3.3.2 ZYNQ程序运行结果

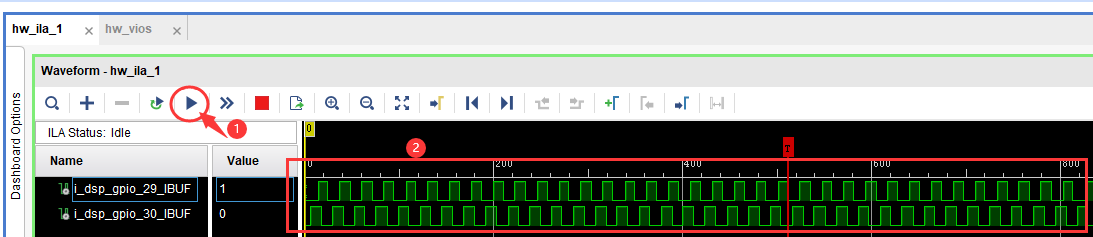

点击hw_ila_1窗口上三角符号的采集触发按钮,如下图①处标识的按钮,可查看到DSP通过GPIO29、GPIO30两个GPIO管脚发过来的方波信号:

1.1.3.4 退出实验

CCS软件窗口上,点击Terminate断开DSP仿真器与板卡的连接。

Vivado调试界面Hardware Manager窗口,右键单击localhost(1),在弹出的菜单中点击Close Server,断开ZYNQ JTAG仿真器与板卡的连接。

最后,关闭板卡电源,实验结束。

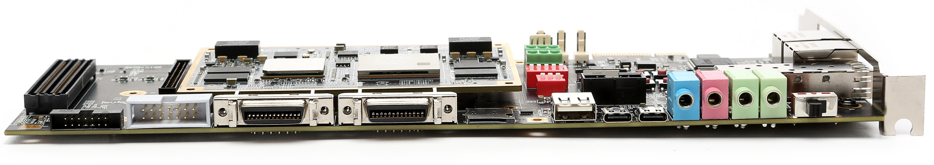

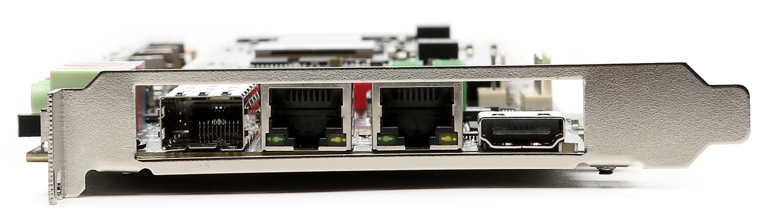

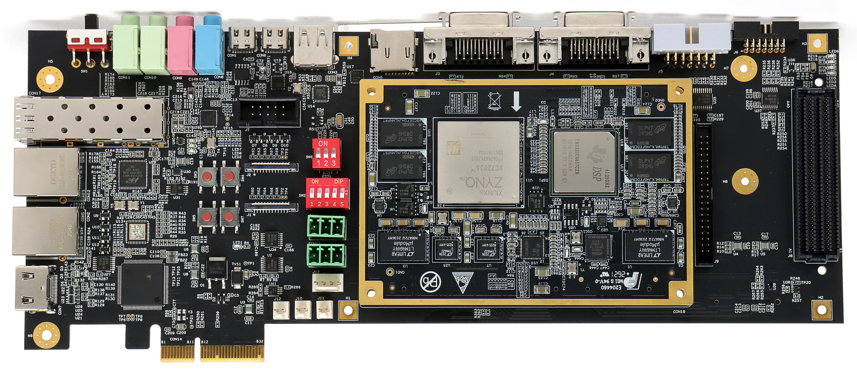

XQ6657Z35-EVM 开发平台

广州星嵌电子科技有限公司自主研发,采用TI DSP TMS320C6657和Xilinx ZYNQ XC7Z035-2FFG676I设计而成。

适用于无人机蜂群、软件无线电系统,基带信号处理,无线仿真平台,高速图像采集、处理等高端领域。

DSP | 处理器型号TI TMS320C6657,双C66x DSP核,主频1GHz/1.25GHz |

|---|---|

Zynq | Xilinx XC7Z035/XC7Z045-2FFG676I(可选)2x ARM Cortex-A9,主频 800MHz(-2)/1GHz(-3),2.5DMIPS/MHz1x Kintex-7 架构可编程逻辑资源 |

CPLD | MAX10型号10M02SCM153 |

FLASH | SPI Flash:32MByte(DSP端)SPI Flash:64MByte(PS端) |

EEPROM | 1Mbit |

DDR3 | DSP DDR3:1GBytesZYNQ DDR3:1GBytes(PS端) |

温度传感器 | TMP102AIDRLT |

CameraLink | 支持2路Base、或者1路Medium、或者1路Full ,支持相机模式(Cameralink图像输出)或采集卡模式(Cameralink图像输入) |

SFP+ | 1路支持万兆光模块 |

千兆网口 | DSP 1路ZYNQ PS 1路 |

PCIe | 1x PCIe 双通道 (DSP端) |

SD | 1x Micro SD(PS端) |

USB | 1x USB 2.0(PS端) |

DSP IO | 38个 |

M.2 | 1x 可接SATA、4G、5G模块(PL端) |

HDMI | 1x HDMI OUT (PL端) |

音频 | 1x LINE IN1x MIC IN1x LINE OUT |

LPC FMC | 1路(PL端) |

电源接口 | 1x TYPE-C接口 12V@4A标准PCIe供电 |

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。